Subject leader: Deyneka Ivan.

Field of study: Master-Study in Technical Physics.

Media of instruction: Slides, board, PC-workstation, programming test facility.

Study plan:

| Week number | Content | Additional information |

| Week 1 |

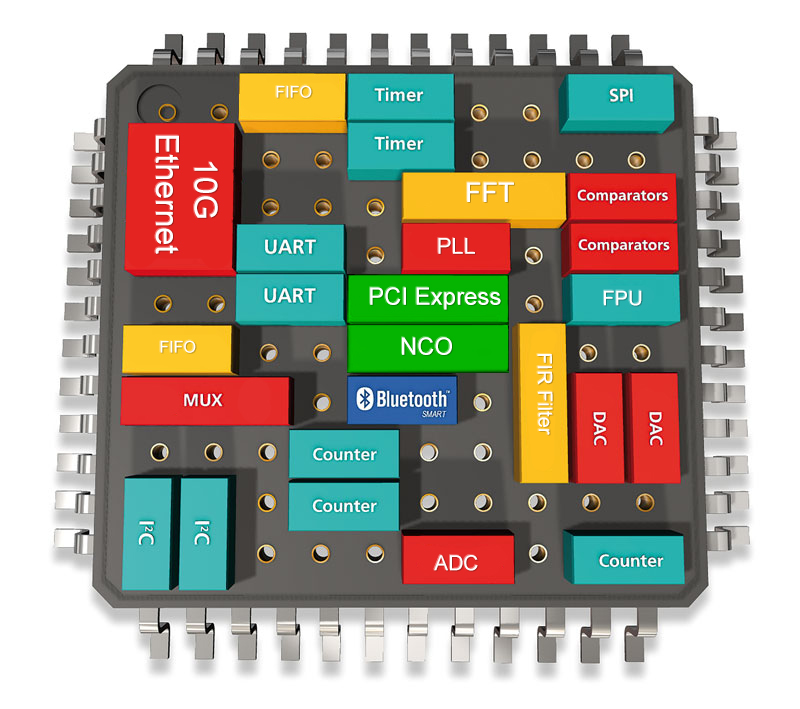

Overview of computer architecture. Layers of abstraction.Basic functional blocks. Memory types. Hierarchy of inputs and outputs. Typical processor architecture. Assembler. Microarchitecture of processors. Pipelined processors. |

Overview lectures, test. |

| Week 2 | ||

| Week 3 | ||

| Week 4 | Introducing Nios II Soft Processor Core/Cortex A9, Eclipse/DS-5, HAL. | Lectures, labs, test. |

| Week 5 | ||

| Week 6 | Interrupts using Interval Timer and GPIO | Lectures, labs, test. |

| Week 7 | Using FPGA part to create custom accelerators. | Lectures, labs, test. Exam. |

| Week 8 |

Examination procedure: examination test or report in written form, homework or other alternative examination. Calculation and graphical tasks. Modeling the specific integrated optical components

Related information:

- https://www.intel.com/content/www/us/en/products/programmable.html - Intel FPGA main webpage

- arm.com - ARM main webpage

- Dr Chu's web - great materials for VHDL and Verilog practice by Chu P.

- Circuit simulator - elecronic circuit simulator

- Digital Design and Computer Architecture by Harris and Harris in Russian and English

For additional information please, contact me via e-mail: vanodnk@yandex.ru, igdeyneka@corp.ifmo.ru